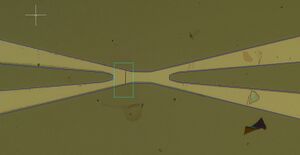

Ge/Al Mesa

Initial Substrate and Design

A stack of Ge-based crystal films are deposited via MBE, and 50 nm of Al is deposited via ALD to create the initial Ge/Al substrate.

This design was originally fabricated at the University of Arkansas. There, the μMLA photolithography system is outside of the gloveboxes, so materials are exposed to oxygen in this process.

In-house Fabrication

To pattern the mesa, a single-layer resist is used: after a 2-minute 110° C pre-bake, the Ge/Al chip is spun with AZ 1505 photoresist at 4000 rpm for 1 minute, then baked again at 110° C for 1 minute.[1] The etch mask is then patterned with the μMLA at a dose of 40 mL/cm2 using the design file in Box. Afterwards, the chip is baked for a final 1 minute at 110° C, then developed for 30 seconds with AZ 300 developer. The aluminum layer is etched by dipping the patterned chip into aluminum etchant for 1 minute and MIF 319 for 2 minutes, 30 seconds. The chip is then placed in Remover PG for 24 hours to remove the etch mask. To create the thin gap in the center of the design, PPA is used as the etch mask. After a 2-minute prebake, 2% wt PPA is spun onto the chip at 2000 rpm for 75 seconds, then baked again for 2 minutes. The NanoFrazor is used to make a small line in the PPA at the location of the gap, and the aluminum etch procedure above is repeated, with 6 minutes in acetone to remove the excess PPA. A flake of hBN (hexagonal boron nitride) is then transferred onto the gap.[2] An inverse pattern is used cover the large bond pads and hBN flake using the single layer resist recipe above; 200 nm of SiO2 is deposited onto the chip via electron beam evaporation, covering everything except the bond pads and flake. After Remover PG is used to remove excess AZ 1505, a top gate is patterned onto the chip--using the single-layer resist outlined above--then 5 nm of Cr and 90 nm of Au are evaporated onto the chip to contact the hBN.

- Mesa design files

See Also

- Handling liquids in a vacuum environment

- Automated Stacker